STM32F103xx系列通用单片机

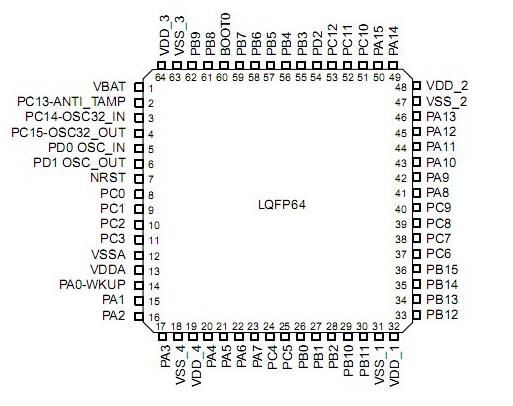

STM32F103CBT6外形图 STM32F103RBT6引脚图

STM32F103xx增强型系列由意法半导体集团设计,使用高性能的ARMCortex-M332位的RISC内核,工作频率为72MHz,内置高速存储器(高达128K字节的闪存和20K字节的SRAM),丰富的增强I/O端口和联接到两条APB总线的外设。所有型号的器件都包含2个12位的ADC、3个通用16位定时器和一个PWM定时器,还包含标准和先进的通信接口:多达2个I2C和SPI、3个USART、一个USB和一个CAN。

一、结构与功能

■内核:ARM32位的Cortex™-M3CPU −72MHz,1.25DMips/MHz(Dhrystone2.1),0等待周期的存储器 −支持单周期乘法和硬件除法

■存储器 −从32K字节至512K字节的闪存程序存储器(STM32F103xx中的第二个x表示FLASH容量,其中:“4”=16K,“6”=32K,“8”=64K,B=128K,C=256K,D=384K,E=512K) −从6K字节至64K字节的SRAM

■时钟、复位和电源管理 −2.0至3.6伏供电和I/O管脚 −上电/断电复位(POR/PDR)、可编程电压监测器(PVD) −内嵌4至16MHz高速晶体振荡器 −内嵌经出厂调校的8MHz的RC振荡器 −内嵌40kHz的RC振荡器 −PLL供应CPU时钟 −带校准功能的32kHzRTC振荡器

■低功耗 −睡眠、停机和待机模式 −VBAT为RTC和后备寄存器供电

■2个12位模数转换器,1us转换时间(16通道) −转换范围:0至3.6V −双采样和保持功能 −温度传感器

■DMA −7通道DMA控制器 −支持的外设:定时器、ADC、SPI、I2C和USART

■多达80个快速I/O口 −26/37/51/80个多功能双向5V兼容的I/O口 −所有I/O口可以映像到16个外部中断 《智能仪表》网络作业

■调试模式 −串行线调试(SWD)和JTAG接口

■多达7个定时器 −多达3个16位定时器,每个定时器有多达4个用于输入捕获/输出比较/PWM或脉冲计数的通道 −16位6通道高级控制定时器 −多达6路PWM输出 −死区控制、边缘/中间对齐波形和紧急制动 −2个看门狗定时器(独立的和窗口型的) −系统时间定时器:24位自减型

■多达9个通信接口 −多达2个I2C接口(SMBus/PMBus) −多达3个USART接口,支持ISO7816,LIN,IrDA接口和调制解调控制 −多达2个SPI同步串行接口(18兆位/秒) −CAN接口(2.0B主动) −USB2.0全速接口

■ECOPACK®封装(兼容RoHS)

二、特点概述

1. ARM®的Cortex™-M3核心

ARM的Cortex-M3处理器是最新一代的嵌入式ARM处理器,它为实现MCU的需要提供了低成本的平台、缩减的管脚数目、降低的系统功耗,同时提供卓越的计算性能和先进的中断系统响应。

ARM的Cortex-M3是32位的RISC处理器,提供额外的代码效率,通常在8和16位系统的存储空间上得以体现ARM核心的高性能。 STM32F103xx增强型系列拥有内置的ARM核心,因此它与所有的ARM工具和软件兼容。

2. 嵌入式Flash存储器和RAM存储器

最新STM32F103xE型拥有高达512K字节的内置闪存存储器,用于存放程序和数据。 多达64KB的嵌入式SRAM可以以CPU的时钟速度进行读写(不待等待状态)。

3. 模拟/数字转换器(ADC)

STM32F103xx增强型产品内嵌2个12位的模拟/数字转换器(ADC),每个ADC有多达16个外部通道,可以实现单次或扫描转换。在扫描模式下,转换在选定的一组模拟输入上自动进行。 ADC接口上额外的逻辑功能允许:

1)、同时采样和保持;

2)、交叉采样和保持;

3)、单次采样。

模拟看门狗功能允许非常精准地监视一路、多路或所有选中的通道,当被监视的信号超出预置的阀值时,将产生中断。由标准定时器(TIMx)和高级控制定时器(TIM1)产生的事件,可以分别内部级联到ADC的开始触发、外部触发和DMA触发,以使应用程序能同步AD转换和时钟。

4. 可变静态存储器(FSMC)

FSMC嵌入在STM32F103xC,STM32F103xD,STM32F103xE中,带有4个片选,支持一下模式:Flash、RAM、PSRAM、NOR和NAND。3个FSMC中断线经过OR后连接到NVIC。没有读/写FIFO,除PCCARD之外,代码都是从外部存储器执行,不支持Boot,目标频率等于SYSCLK/2,所以当系统时钟是72MHz时,外部访问按照36MHz进行。

5. 嵌套矢量中断控制器(NVIC)

可以处理43个可屏蔽中断通道(不包括Cortex-M3的16根中断线),提供16个中断优先级。紧密耦合的NVIC实现了更低的中断处理延迟,直接向内核传递中断入口向量表地址,紧密耦合的NVIC内核接口,允许中断提前处理,对后到的更高优先级的中断进行处理,支持尾链,自动保存处理器状态,中断入口在中断退出时自动恢复,不需要指令干预。

6. 外部中断/事件控制器(EXTI)

外部中断/事件控制器由用于19条产生中断/事件请求的边沿探测器线组成。每条线可以被单独配置用于选择触发事件(上升沿,下降沿,或者两者都可以),也可以被单独屏蔽。有一个挂起寄存器来维护中断请求的状态。当外部线上出现长度超过内部APB2时钟周期的脉冲时,EXTI能够探测到。多达112个GPIO连接到16个外部中断线。

三.时钟和启动

在启动的时候还是要进行系统时钟选择,但复位的时候内部8MHz的晶振被选用作CPU时钟。可以选择一个外部的4-16MHz的时钟,并且会被监视来判定是否成功。在这期间,控制器被禁止并且软件中断管理也随后被禁止。同时,如果有需要(例如碰到一个间接使用的晶振失败),PLL时钟的中断管理完全可用。多个预比较器可以用于配置AHB频率,包括高速APB(PB2)和低速APB(APB1),高速APB最高的频率为72MHz,低速APB最高的频率为36MHz。 Boot模式 在启动的时候,Boot引脚被用来在3种Boot选项种选择一种:从用户Flash导入,从系统存储器导入,从SRAM导入。Boot导入程序位于系统存储器,用于通过USART1重新对Flash存储器编程。

四.电源供电方案

VDD,电压范围为2.0V-3.6V,外部电源通过VDD引脚提供,用于I/O和内部调压器。VSSA和VDDA,电压范围为2.0-3.6V,外部模拟电压输入,用于ADC,复位模块,RC和PLL,在VDD范围之内(ADC被限制在2.4V),VSSA和VDDA必须相应连接到VSS和VDD。